# Electrical Properties of Low-Temperature-Compatible P-Channel Polycrystalline-Silicon TFTs Using High- $\kappa$ Gate Dielectrics

Ming-Jui Yang, Chao-Hsin Chien, *Associate Member, IEEE*, Yi-Hsien Lu, Chih-Yen Shen, and Tiao-Yuan Huang, *Fellow, IEEE*

Abstract—In this paper, we describe a systematic study of the electrical properties of low-temperature-compatible p-channel polycrystalline-silicon thin-film transistors (poly-Si TFTs) using  $HfO_2$  and  $HfSiO_x$  high- $\kappa$  gate dielectrics. Because of their larger gate capacitance density, the TFTs containing the high- $\kappa$ gate dielectrics exhibited superior device performance in terms of higher  $I_{\rm on}/I_{\rm off}$  current ratios, lower subthreshold swings (SSs), and lower threshold voltages  $(V_{\rm th})$ , relative to conventional deposited-SiO2, albeit with slightly higher OFF-state currents. The TFTs incorporating  $HfSiO_x$  as the gate dielectric had ca. 1.73 times the mobility  $(\mu_{\rm FE})$  relative to that of the deposited-SiO2 TFTs; in contrast, the HfO2 TFTs exhibited inferior mobility. We investigated the mechanism for the mobility degradation in these  $HfO_2$  TFTs. The immunity of the  $HfSiO_x$ TFTs was better than that of the HfO2 TFTs-in terms of their  $V_{

m th}$  shift, SS degradation,  $\mu_{

m FE}$  degradation, and drive current deterioration—against negative bias temperature instability stressing. Thus, we believe that  $HfSiO_x$ , rather than  $HfO_2$ , is a potential candidate for use as a gate-dielectric material in future high-performance poly-Si TFTs.

Index Terms—Hafnium silicate (HfSiO $_x$ ), high dielectric constant (high- $\kappa$ ), negative bias temperature instability (NBTI), polycrystalline-silicon thin-film transistors (poly-Si TFTs).

# I. INTRODUCTION

OLYCRYSTALLINE-SILICON thin-film transistors (poly-Si TFTs) are employed extensively in active-matrix liquid crystal displays because of their superior performance [1]. Recently, the practicability of integrating the entire system on the panel has been investigated vigorously [2].

Manuscript received September 21, 2007; revised December 26, 2007. This work was supported in part by the National Science Council, Taiwan, R.O.C., under Contract 95-2221-E-009-313. The review of this paper was arranged by Editor M. J. Kumar.

- M.-J. Yang and C.-H. Chien are with the Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu 300, Taiwan, R.O.C. and also with the National Nano Device Laboratory, Hsinchu 300, Taiwan, R.O.C. (e-mail: chchien@mail.ndl.org.tw; chchien@faculty.nctu.edu.tw).

- Y.-H. Lu is with the Institute of Electrophysics, National Chiao Tung University, Hsinchu 300, Taiwan, R.O.C.

- C.-Y. Shen is with the National Nano Device Laboratory, Hsinchu 300, Taiwan, R.O.C.

- T.-Y. Huang is with the Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu 300, Taiwan, R.O.C.

- Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org

Digital Object Identifier 10.1109/TED.2008.916759

This goal requires that the display driving circuits contain high-performance TFTs capable of operating at lower voltages while delivering higher drive currents. Although scaling down the gate oxide can increase the drive current of a TFT, it leads inevitably to a higher gate leakage current because of the decreased quality of the low-temperature-deposited gate dielectrics [3]. To maintain the physical dielectric thickness while increasing the gate capacitance, several new high- $\kappa$ materials have been proposed, including Al<sub>2</sub>O<sub>3</sub>, Ta<sub>2</sub>O<sub>5</sub>, and HfO<sub>2</sub> [4]-[6]. Because Al<sub>2</sub>O<sub>3</sub> films exhibit relatively low values of  $\kappa$  (ca. 7) and excess fixed charge, the TFT performance is not improved sufficiently for application [7]. The narrow band-gap of Ta<sub>2</sub>O<sub>5</sub> means that a thicker film is necessary to reduce the gate leakage current of TFTs [8], which limits the increase in gate capacitance. Recently, hafnium dioxide (HfO<sub>2</sub>) has been applied to TFTs because of its high value of  $\kappa$  (14 to 20) and sufficiently wide band-gap [6]. Although poly-Si TFTs incorporating HfO2 as the gate dielectric exhibit superior performance in many respects, several issues remain problematic, e.g., the higher gate leakage current arising from polycrystalline HfO2 films and the degraded mobility arising from additional scattering. In this paper, we employed HfO2 and HfSiOx as gate dielectrics for p-channel poly-Si TFTs and found that the transistors containing high- $\kappa$  dielectrics exhibited higher values of  $I_{\rm on}/I_{\rm off}$ and  $\mu_{\rm FE}$  and smaller values of subthreshold swing (SS) and  $V_{\rm th}$ , relative to transistors containing a conventional deposited-SiO<sub>2</sub> dielectric. We also studied the instability of these TFTs under negative bias temperature instability (NBTI) stress. By measuring and analyzing the transfer characteristics before and after stressing for various stress times and temperatures, we determined the effects of NBTI on the poly-Si TFTs incorporating high- $\kappa$  dielectrics.

# II. DEVICE FABRICATION

Self-aligned top-gated p-channel poly-Si TFTs were fabricated. First, a 550-nm-thick thermal oxide was grown on Si wafers in a furnace to simulate the glass substrate. Next, a 100-nm-thick amorphous-silicon layer was deposited through the dissociation of SiH $_4$  gas in a low-pressure chemical-vapor-deposition (LPCVD) system at 550 °C. Subsequently, solid-phase crystallization was performed at 600 °C for 24 h in N $_2$

ambient to induce the crystallization of amorphous silicon. Individual active regions were then patterned by lithography and defined by dry etching. After cleaning, various gate dielectrics (each 60-nm thick) were deposited. Specifically, HfO2 and  $HfSiO_x$  films were deposited through atomic-vapor deposition using an AIXTRON Tricent System at a substrate temperature of 500 °C. The Hf[OC(CH<sub>3</sub>)<sub>3</sub>]<sub>2</sub>(mmp)<sub>2</sub> precursor, Si(mmp)<sub>4</sub> precursor, and oxygen gas were employed as Hf, Si, and O sources, respectively. The as-deposited oxide, which served as the control sample, was prepared through LPCVD at 700 °C using tetraethyloxysilane as the precursor. All of the wafers were then subjected to deposition of a 300-nm-thick amorphoussilicon layer, which served as the gate electrode, through LPCVD at 550 °C. The gate electrodes were patterned, and the source, drain, and gate regions were doped through self-aligned boron ion implantation (dosage:  $5 \times 10^{15}$  ions/cm<sup>2</sup>; energy: 15 keV). After the formation of the source and drain, the dopant was activated at 600 °C for 24 h in N<sub>2</sub> ambient. Following that, 500-nm SiO<sub>2</sub> was deposited by plasma-enhanced CVD as the interlayer dielectric. Finally, contact holes were opened, and 550-nm AiSiCu alloy was deposited and defined. The wafers were then sintered at 400 °C for 30 min in forming gas to complete the fabrication. Capacitors containing high- $\kappa$  dielectrics were fabricated simultaneously through the use of a shadow mask to allow measurement of dielectric constants and leakage current densities. Device measurements were performed using a Keithley 4200 semiconductor characterization system, an HP 4156A precision semiconductor parameter analyzer, and an Agilent 4284A precision LCR meter. The field-effect mobility, which was extracted from the maximum transconductance  $(G_{\rm m})$ , and the SS were measured at a value of  $V_{\rm DS}$  of -0.1 V. The value of the SS was extracted from the maximum slope of the  $I_{\rm DS} - V_{\rm GS}$  characteristics. The threshold voltage was defined as the gate voltage at which the drain-current reached a normalized drain-current  $(I_D)$  equal to  $(W/L) \times 10^{-8}$  A at a value of  $V_{\rm DS}$  of -0.1 V, where W is the drawn channel width and L is the drawn channel length. During NBTI stressing, the substrate was heated to the stress temperature (ranging from 25 °C to 100 °C), and then, the stress bias of 2 MV/cm was applied to the gate with the source and drain grounded. The stress was removed periodically to measure the basic device characteristics and to characterize the NBTI effect; all measurements were performed at the stress temperature.

# III. RESULTS AND DISCUSSION

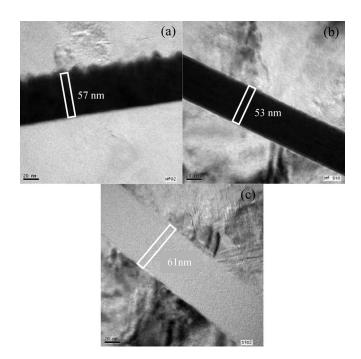

Fig. 1 shows cross-sectional transmission-electron-microscopy (TEM) images of the  $HfO_2$ ,  $HfSiO_x$ , and deposited- $SiO_2$  films, which had physical thicknesses of 57, 53, and 61 nm, respectively. The  $HfSiO_x$  and deposited- $SiO_2$  films both possessed amorphous structures, which were conducive to forming smoother surfaces at both the top and bottom interfaces, whereas the  $HfO_2$  film revealed a polycrystalline structure. Atomic-force microscopy revealed similar features (data not shown). The mean surface roughnesses of the  $HfSiO_x$  and deposited- $SiO_2$  films were 0.42 and 0.60 nm, respectively—much smaller than that (1.97 nm) of the  $HfO_2$  film. For further analysis, we used X-ray diffraction

Fig. 1. Cross-sectional TEM images of TFTs incorporating (a)  $HfO_2$ , (b)  $HfSiO_x$ , and (c) deposited- $SiO_2$  gate dielectrics.

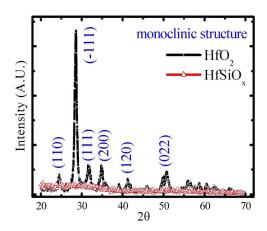

Fig. 2. X-ray diffraction patterns of HfO $_2$  and HfSiO $_x$  films after annealing for 24 h at 600  $^{\circ}$ C in a N $_2$  ambient.

spectroscopy (XRD) to investigate the crystallinity of the  $HfO_2$  and  $HfSiO_x$  films (Fig. 2). After annealing at  $600\,^{\circ}\mathrm{C}$  and 24 h in a  $N_2$  ambient, the  $HfO_2$  film clearly exhibited a polycrystalline monoclinic structure, whereas the  $HfSiO_x$  film retained its amorphous form. This behavior suggests that the  $HfSiO_x$  film had better thermal stability than did the  $HfO_2$  film.

Fig. 3(a) and (b) provide plots of the capacitance density versus the gate voltage and the leakage-current density versus the electrical field, respectively, for the high- $\kappa$  dielectrics. The extracted value of  $\kappa$  for the HfO<sub>2</sub> film was ca. 14.2, which is significantly lower than that of bulk HfO<sub>2</sub>, possibly because of the following reasons: 1) the presence of excess oxygen atoms in the HfO<sub>2</sub> film [9] and 2) the fact that the mode effective charges associated with the softest modes are relatively weak when the HfO<sub>2</sub> film possesses its most stable monoclinic structure [10], [11]. On the other hand, the value of  $\kappa$  for the HfSiO<sub>x</sub> film was

Fig. 3. Plots of (a) capacitance density versus gate voltage and (b) leakage-current density versus electrical field for the  $HfO_2$  and  $HfSiO_x$  films obtained after annealing for 24 h at 600 °C in a  $N_2$  ambient.

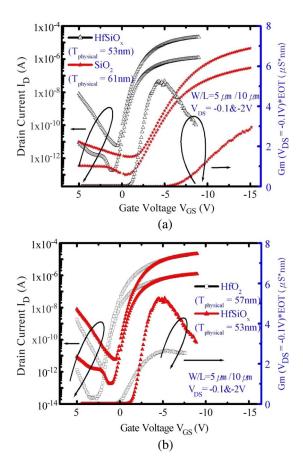

ca. 8.11, which is also lower than expected. The Hf/Si composition ratio (ca. 1:1.44) calculated from this value of  $\kappa$  was close to that (1:1.38) measured using electron spectroscopy for chemical analysis (ESCA; data not shown). This result indicates that Si atoms are more reactive toward oxygen atoms than are Hf atoms under our process conditions; therefore, the lower dielectric constant of the HfSiO<sub>x</sub> films is due to their being Si-rich. In terms of the films' current-voltage characteristics, the HfSiO<sub>x</sub> film exhibited superior performance—a smaller leakage current  $(7.60 \times 10^{-8} \text{ A/cm}^2 \text{ at } V_{\rm GS} = -10 \text{ V})$  and a larger breakdown field (-7 MV/cm)—relative to that of the  $HfO_2$  film  $(4.70 \times 10^{-9} \text{ A/cm}^2 \text{ and } -4 \text{ MV/cm}, \text{ respectively}),$ presumably because of the amorphous nature of  $HfSiO_x$  after processing. Fig. 4(a) and (b) provide comparisons of the transfer characteristics between the TFTs containing HfSiO<sub>x</sub> and deposited-SiO<sub>2</sub> and between the TFTs containing  $HfSiO_x$  and HfO<sub>2</sub>, respectively, at values of  $V_{\rm DS}$  of -0.1 and -2 V. Table I summarizes the measured data and the extracted device parameters. The TFTs containing the high- $\kappa$  dielectrics displayed considerably better performance than did the TFT containing the conventional deposited-SiO2, with the exception of their OFF-state leakage currents. In addition to the superior quality of the gate-dielectric-poly-Si interface [5], we believe that the thinner equivalent oxide thicknesses of the high- $\kappa$  dielectrics at the same physical thickness accounts for the lower value of  $V_{\rm th}$  and the significantly improved SS [12], [13]. Moreover,

Fig. 4. Comparisons of the transfer characteristics at values of  $V_{\rm DS}$  of -0.1 and -2 V between the TFTs containing (a) HfSiO $_x$  and deposited-SiO $_2$  and (b) HfSiO $_x$  and HfO $_2$  as gate dielectrics.

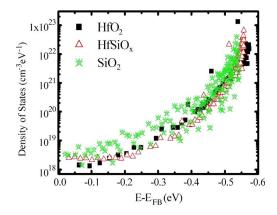

we have reported previously that the values of  $V_{\rm th}$  and SS are sensitive to the density of deep states near the midgap; i.e., as the densities-of-state decreases, the values of  $V_{\rm th}$  and SS decrease [14]. This behavior is supported by the plots of the density-of-state versus  $\Delta E$  (where  $\Delta E = E - E_{\rm FB}$ ) for the poly-Si TFTs incorporating the various gate dielectrics (Fig. 5). The values of densities-of-state were extracted from the transfer characteristics measured at 25 °C, 50 °C, 75 °C, 100 °C, and 125 °C [15]. We found that the high- $\kappa$  dielectrics did possess lower densities-of-state. On the other hand, the effective interface-trap-state density  $(N_{\rm it})$  near the poly-Si-gate-dielectric interface can be evaluated from the value of SS [16]

$$N_{\rm it} = \left[ \left( \frac{S}{\ln 10} \right) \left( \frac{q}{kT} \right) - 1 \right] \left( \frac{C_{\rm gate \ dielectric}}{q} \right). \tag{1}$$

The calculated values of  $N_{\rm it}$  for the HfO<sub>2</sub>, HfSiO<sub>x</sub>, and deposited-SiO<sub>2</sub> TFTs were  $5.60\times10^{12}$ ,  $4.44\times10^{12}$ , and  $7.86\times10^{12}/{\rm cm^2}$ , respectively. Thus, this approach also reveals that the high- $\kappa$  dielectrics possess lower densities-of-state relative to that of the deposited-SiO<sub>2</sub>.

Although the values of the SS and  $I_{\rm on}/I_{\rm off}$  current ratio of the TFTs containing  ${\rm HfSiO}_x$  were slightly worse than those of the TFTs incorporating  ${\rm HfO}_2$ , we believe that  ${\rm HfSiO}_x$  is the better choice for use as the gate dielectric in future poly-Si TFTs for the following reasons. First, the TFTs containing  ${\rm HfSiO}_x$  films exhibited the smaller leakage-current densities

|                                                            |                                              |                  |             | 20                                       |             |

|------------------------------------------------------------|----------------------------------------------|------------------|-------------|------------------------------------------|-------------|

| Gate dielectric                                            | $I_{on}/I_{off}$ ratio<br>(@ $V_{DS}$ = -2V) | S. S.<br>(V/Dec) | $V_{th}(V)$ | μ <sub>FE</sub> (cm <sup>2</sup> /V-sec) | EOT<br>(nm) |

| $ (T_{\text{physical}} = 57 \text{nm}) $                   | 8.95E6<br>(V <sub>GS</sub> = -8V)            | 0.30             | 0.25        | 15.37                                    | 15.7        |

| $HfSiO_{x}$ $(T_{physical} = 53nm)$                        | 3.79E6<br>(V <sub>GS</sub> = -8V)            | 0.37             | -1.13       | 30.41                                    | 25.5        |

| Deposited-SiO <sub>2</sub> $(T_{physical} = 61 \text{nm})$ | 3.65E6<br>(V <sub>GS</sub> = -15V)           | 1.06             | -6.90       | 17.61                                    | 46.5        |

TABLE I Device Parameters of Low-Temperature P-Channel Poly-Si TFTs  $(W/L=5~\mu{\rm m}/10~\mu{\rm m})$  Incorporating Various Gate Dielectrics at a Value of  $V_{\rm DS}$  of  $-0.1~{\rm V}$

Fig. 5. Densities-of-state extracted from the transfer characteristics ( $V_{\rm DS} = -0.1~{\rm V}$ ) of poly-Si TFTs incorporating various gate dielectrics.

TABLE II

ETCHING RATES OF VARIOUS GATE DIELECTRICS

| Gate dielectric            | BOE etching | ICP dry etcher                    |                 |  |

|----------------------------|-------------|-----------------------------------|-----------------|--|

| Gate dielectric            | BOE etching | CF <sub>4</sub> /CHF <sub>3</sub> | $\mathrm{Cl}_2$ |  |

| HfO <sub>2</sub>           | 0 nm/sec    | 0.4 nm/sec                        | 1.3 nm/sec      |  |

| HfSiO <sub>x</sub>         | 0.65 nm/sec | 1.1 nm/sec                        | 2.6 nm/sec      |  |

| Deposited-SiO <sub>2</sub> | 10 nm/sec   | 6.5 nm/sec                        | 3.5 nm/sec      |  |

and larger breakdown fields than did the HfO2 TFTs because of the amorphous nature of the  $HfSiO_x$  film after processing. Second, the hole mobility of the TFTs containing  $HfSiO_x$  was 73% better than that of the conventional TFTs incorporating the deposited-SiO<sub>2</sub> dielectric, whereas it was worse for the TFTs containing HfO<sub>2</sub>. According to previous reports [17]-[19], we speculate that the degraded mobility of the TFTs containing the HfO<sub>2</sub> dielectric is due to additional Coulomb scattering caused by the charges in the HfO<sub>2</sub> dielectric. In conventional MOSFETs, additional Coulomb scattering is closely related to the polycrystalline structure of the HfO<sub>2</sub> films, which in turn leads to severe mobility degradation in devices possessing physically thicker HfO<sub>2</sub> films [18]. In contrast, HfSiO<sub>x</sub> films prevent this additional scattering and exhibit improved mobility because of their higher thermal stability. Third, the removal of  $HfSiO_x$  through etching is much easier than that of  $HfO_2$ . This feature is rather important for device fabrication. We employed a buffer-oxide-etch (BOE) solution and an inducedcoupling-plasma (ICP) etcher to perform wet and dry etching, respectively. Table II summarizes the etching rates for the various dielectrics when using the two etching methods and various gases. The  $HfO_2$  film could not be etched away; its thickness remained nearly constant after wet etching for 1 min. For dry etching, we found that the etching rate for  $HfO_2$  film with  $CF_4/CHF_3$  mixing gas (0.4 nm/s) was much lower than that for the deposited  $SiO_2$  (6.5 nm/s). Even though the etching rate could be increased to 1.3 nm/s when using  $Cl_2$  gas, the poly-Si channel was more vulnerable to etching damage because of its relatively high etching rate of 3 nm/s. In contrast, the  $HfSiO_x$  films could be removed by the BOE solution at a rate of 0.65 nm/s, and the dry etching rates were also faster than those of the  $HfO_2$  films. As a result, less etching damage occurs at the  $HfSiO_x$ -film-poly-Si interface of contact regions when using a sequence of dry etching followed by wet etching near the end of the etching process.

Although the TFTs incorporating the high- $\kappa$  gate dielectrics exhibited better ON-state electrical properties than did the conventional TFT containing deposited-SiO<sub>2</sub>, much more severe effects of gate-induced drain leakage (GIDL) were clearly evident in the plots of the transfer characteristics of the high- $\kappa$ TFTs. To further clarify the mechanism of the larger OFF-state current, the activation energies of the different gate dielectrics were calculated from the  $I_{\rm DS}$ - $V_{\rm GS}$  curves obtained at 25 °C, 50 °C, 75 °C, 100 °C, and 125 °C. Fig. 6(a) and (b) present plots of the dependence of activation energy  $(E_a)$  on  $V_{GS}$  at values of  $V_{\rm DS}$  of -0.1 and -2 V, respectively. At the lower value of  $V_{\rm DS}$ , the TFT containing HfO<sub>2</sub> had the highest activation energy accounting for the depicted lowest minimum leakage current. Upon increasing  $|V_{GS}|$  in the OFF-state regime, the activation energy of the TFT incorporating HfO<sub>2</sub> decreased drastically, whereas those containing  $HfSiO_x$  and deposited  $SiO_2$  exhibited smooth decreases in their activation energies. When the value of  $V_{\rm DS}$  was -2 V, all of the TFTs exhibited rapidly decreasing values of  $E_a$  upon increasing  $|V_{GS}|$ . To explain these results, we must consider the leakage mechanisms of the poly-Si TFTs in the OFF-state [20]-[24]. Typically, the OFF-state current in the poly-Si TFTs can be divided into the following three parts: 1) in the region of very low  $|V_{\rm GS}|$ , the increasing OFF-state current as  $|V_{GS}|$  increases is related to the resistive current, which is assumed to be an ohmic current flowing through the poly-silicon layer; 2) in the almost-flat region, the OFF-state current that does not change with increasing  $|V_{GS}|$  is related to the thermal-generation current, which was reported to be nearly independent of  $|V_{GS}|$  [20]; and 3) in the high- $|V_{GS}|$  region, the increasing OFF-state current as  $|V_{\rm GS}|$  increases is linked to the thermionic field or Frenkel-Poole emission current, which is due to field-enhanced thermal excitation. In Fig. 4, we observe

Fig. 6. Channel activation energies obtained from the temperature dependence of the transfer characteristics of the poly-Si TFTs incorporating various gate dielectrics at values of  $V_{\rm DS}$  of (a) -0.1 and (b) -2 V.

clearly that the OFF-state current was dominated by the resistive current and thermal-generation current for the TFTs containing deposited-SiO<sub>2</sub> gate dielectrics at a value of  $V_{\rm DS}$  of -0.1 V. When  $V_{\rm DS}$  was increased to -2 V, the thermal-generation current prevailed in the low- $|V_{\rm GS}|$  regime, and the Frenkel-Poole emission current preponderated in the high- $|V_{GS}|$  regime. On the other hand, we found that the OFF-state currents in the HfSiO<sub>x</sub> TFTs at a value of  $V_{\rm DS}$  of -0.1 V were resistive, thermal generation, and Frenkel-Poole emission currents in the low-, intermediate-, and high- $|V_{\rm GS}|$  ranges, respectively; in contrast, only the Frenkel-Poole emission current was present when  $V_{\rm DS}$  was -2 V for the all of the  $|V_{\rm GS}|$  ranges. The HfO<sub>2</sub> TFTs exhibited similar behavior, although the Frenkel-Poole emission current prevailed over the other two currents, even when  $V_{\rm DS}$  was -0.1 V. We speculate that these results are closely related to the higher values of  $\kappa$  possessed by the high- $\kappa$  dielectrics. According to the Frenkel–Poole emission mechanism, the OFF-state current is highly dependent on the peak electric field  $(E_{\rm pk})$  at the drain junction and is dominated by the vertical electric field at the interface; thus

$$I_{\rm FE} \propto \exp(\sqrt{E_{\rm pk}})$$

$$E_{\rm pk} = \frac{(V_{\rm GS} - V_{\rm DS} - V_{\rm FB})\varepsilon_{\rm gate\,dielectric}}{(T_{\rm gate\,dielectric}\varepsilon_{\rm Si})}$$

(2)

where  $\varepsilon_{\rm Si}$  and  $\varepsilon_{\rm gate\ dielectric}$  are the permittivities of Si and the gate dielectric, respectively,  $V_{\rm FB}$  is the flatband voltage defined as minimum  $I_{\rm DS}$ , and  $T_{\rm gate\ dielectric}$  is the physical thickness of the gate dielectric. The poly-Si TFTs incorporating the high- $\kappa$ gate dielectrics definitely exhibited their higher peak electric fields as a result of their higher values of  $\kappa$  (because the physical thicknesses of all the dielectrics were similar), which then caused the rapidly increasing Frenkel–Poole emission currents. These results can also be explained by considering the plots of the activation energy. At a low drain-to-gate bias  $|V_{\rm DG}|$ , the thermal-generation current was the dominant leakage-current mechanism, and the corresponding value of  $E_a$  was higher. As  $|V_{\rm DG}|$  increased, the Frenkel–Poole emission current gradually became the preeminent leakage mechanism, and the value of  $E_a$ , which was most significant to the thermal-generation current, decreased rapidly. As a result, we suggest that lightly doped drain, multigate, and offset structures, which can reduce the electrical field between the drain and the channel of the TFT, could be applied to suppress the deterioration of the OFF-state current when high- $\kappa$  dielectrics are employed as gate dielectrics.

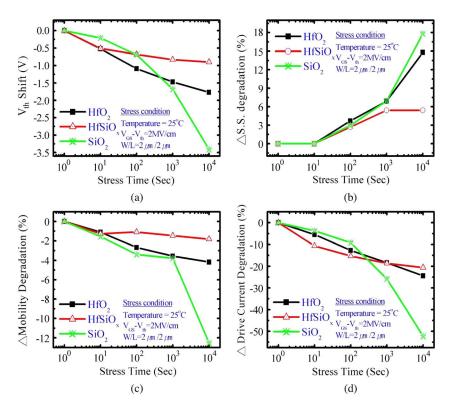

We also studied the instability of the low-temperature p-channel poly-Si TFTs possessing the various gate dielectrics under NBTI stress. Fig. 7(a)-(d) display the variations in the values of  $V_{\rm th}$ , SS,  $\mu_{\rm FE}$ , and the drive current as functions of the NBTI-stress time. Initially, the deposited-SiO<sub>2</sub> TFT displayed less of a shift in  $V_{

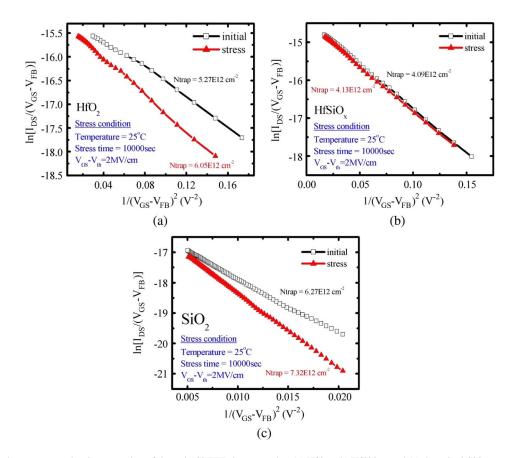

m th}$  and the drive-current degradation than did the other two TFTs. In contrast, the TFTs incorporating the high- $\kappa$  dielectrics exhibited less degradation than did those containing deposited SiO<sub>2</sub> for all of these parameters when the stress period increased; specifically, the HfSiO<sub>x</sub> TFT exhibited the strongest immunity against stress. We believe that these results are closely related to the fact that the trapped charge accumulates in the high- $\kappa$  dielectric via filling, rather than through generation, which occurs in the deposited-SiO<sub>2</sub> [25], [26]. According to previous reports [27]–[30], we attribute the degradation of both SS and  $\mu_{\rm FE}$  mainly to interface-trap-state generation. The NBTI stress, which causes bonds to break at the poly-Si-gate dielectric interface and generates more dangling bonds, results in the increased number of interface trap states. Our results proved that the  $HfSiO_x$  film possessed the superior interface quality; i.e., fewer traps would be created during the application of stress. Based on formula (1), we estimated the  $N_{\rm it}$  increment to be only 6.43% for the HfSiO<sub>x</sub> TFT after stressing. This value was much lower than those for the TFTs containing the HfO<sub>2</sub> and deposited-SiO<sub>2</sub> films (both ca. 19%). In addition, the  $V_{\rm th}$  shift in the poly-Si TFTs caused by the NBTI stress is also governed by the generation of grain-boundary traps in the channel [30]. To investigate the effects of the grain-boundary traps during NBTI stress, we used the Levinson-Proano method to estimate the grainboundary trap densities  $(N_{\text{trap}})$  for all of the samples [31], [32]. Fig. 8(a)–(c) present the plots of  $\ln[I_{\rm DS}/(V_{\rm GS}-V_{\rm FB})]$  versus  $1/(V_{\rm GS}-V_{\rm FB})^2$  at a value of  $V_{\rm DS}$  of -0.1 V and at high  $V_{\rm GS}$ , where the flatband voltage  $(V_{\rm FB})$  is defined as the gate voltage that yields the minimum drain current from the transfer characteristic. We found that the  $HfSiO_x$  TFT not only provided the lowest initial value of  $N_{\rm trap}$  but also the highest immunity

Fig. 7. Values of (a)  $V_{\rm th}$ , (b) SS, (c)  $\mu_{\rm FE}$ , and (d) the drive current of the poly-Si TFTs incorporating various gate dielectrics, plotted with respect to the stress time at 25 °C.

Fig. 8. Grain-boundary trap-state density extraction of the poly-Si TFTs incorporating (a)  $HfO_2$ , (b)  $HfSiO_x$ , and (c) deposited- $SiO_2$  gate dielectrics before and after NBTI stressing for  $10\,000$  s at  $25\,^{\circ}C$ ; stress bias:  $V_{\rm GS}-V_{\rm th}=2\,{\rm MV/cm}$ .

Fig. 9. Values of (a)  $V_{\rm th}$ , (b) SS, (c)  $\mu_{\rm FE}$ , and (d) drive current of the poly-Si TFTs incorporating various gate dielectrics, plotted with respect to the stress time at 100 °C.

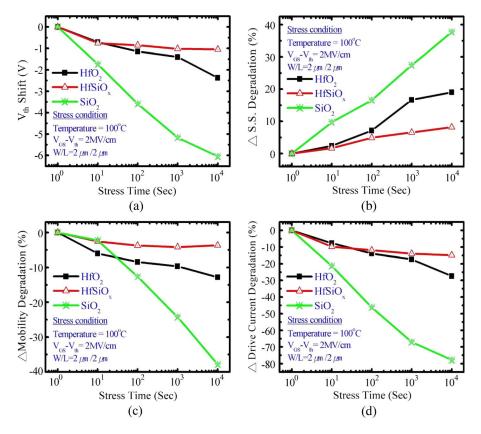

against  $N_{\mathrm{trap}}$  creation during stressing, although the detailed mechanism is not clear at present. As a consequence, we expect less degradation of the drive currents of  $HfSiO_x$  TFTs, because the drive-current degradation is mainly attributed to the  $V_{\rm th}$ shift and the decrease in  $\mu_{\rm FE}$ . Fig. 9(a) and (b) display the variations of  $V_{\rm th}$ , SS,  $\mu_{\rm FE}$ , and the drive current as a function of the NBTI-stress time at 100 °C. Although the tendencies are similar to those revealed at room temperature, we note that the TFTs containing the high- $\kappa$  dielectrics were relatively insensitive to high temperature, whereas the deterioration of the deposited-SiO<sub>2</sub> TFT was dramatic. This feature seems very favorable for TFTs to be fabricated on displays, because glass substrates have very poor thermal conductivity. As a result, using high- $\kappa$ gate dielectrics cannot only enhance the performance of poly-Si TFTs but also improve their reliability over those incorporating conventional deposited-SiO<sub>2</sub>. In addition,  $HfSiO_x$  appears to have better potential over HfO2 for use as a future gate dielectric in low-temperature-compatible poly-Si TFTs.

## IV. CONCLUSION

In this paper, we have demonstrated that low-temperature p-channel poly-Si TFTs incorporating high- $\kappa$  gate dielectrics exhibit improved performance and long-term stability—i.e., higher values of  $\mu_{\rm FE}$  and  $I_{\rm on}/I_{\rm off}$ , smaller values of SS and  $V_{\rm th}$ , and superior NBTI reliability—relative to TFTs containing conventional deposited-SiO<sub>2</sub>. Our results suggest that HfSiO<sub>x</sub> is a more suitable candidate than HfO<sub>2</sub> for use as a gate-dielectric material in future high-performance poly-Si TFTs.

### REFERENCES

- [1] H. Oshima and S. Morozumi, "Future trends for TFT integrated circuits on glass substrates," in *IEDM Tech. Dig.*, 1989, pp. 157–160.

- [2] K. Werner, "The flowering of flat displays," *IEEE Spectrum*, vol. 34, no. 5, pp. 40–49, May 1997.

- [3] A. Takami, A. İshida, J. Tsutsumi, T. Nishibe, and N. Ibaraki, "Threshold voltage shift under the gate bias stress in low-temperature poly-silicon TFT with the thin gate oxide film," in *Proc. Int. Workshop AM-LCD*, Tokyo, Japan, Jul. 2000, pp. 45–48.

- [4] M. Y. Um, S.-K. Lee, and H. J. Kim, "Characterization of thin film transistor using Ta<sub>2</sub>O<sub>5</sub> gate dielectric," in *Proc. Int. Workshop AM-LCD*, Tokyo, Japan, Jul. 1998, pp. 45–46.

- [5] Z. Jin, H. S. Kwok, and M. Wong, "High-performance polycrystalline SiGe thin-film transistors using Al<sub>2</sub>O<sub>3</sub> gate insulators," *IEEE Electron Device Lett.*, vol. 19, no. 12, pp. 502–504, Dec. 1998.

- [6] C.-P. Lin, B.-Y. Tsui, M.-J. Yang, R.-H. Huang, and C.-H. Chien, "High-performance poly-silicon TFTs using HfO<sub>2</sub> gate dielectric," *IEEE Electron Device Lett.*, vol. 27, no. 5, pp. 360–363, May 2006.

- [7] B. W. Busch, O. Pluchery, Y. J. Chabal, D. A. Muller, R. L. Opila, J. R. Kwo, and E. Garfunkel, "Materials characterization of alternative gate dielectrics," MRS Bull., vol. 27, no. 3, pp. 206–211, Mar. 2002.

- [8] H. S. P. Wong, "Beyond the conventional transistor," IBM J. Res. Develop., vol. 46, no. 2/3, pp. 133–168, Mar./May 2002.

- [9] J. F. Conley, Jr., Y. Ono, D. J. Tweet, and W. Zhuang, "Atomic layer deposition of thin hafnium oxide films using a carbon free precursor," *J. Appl. Phys.*, vol. 93, no. 1, pp. 712–718, Jan. 2003.

- [10] X. Zhao and D. Vanderbilt, "First-principles study of structural, vibrational, and lattice dielectric properties of hafnium oxide," *Phys. Rev. B, Condens. Matter*, vol. 65, no. 23, p. 233 106, Jun. 2002.

- [11] T. S. Boscke, S. Govindarajan, C. Fachmann, J. Heitmann, A. Avellan, U. Schroder, S. Kudelka, P. D. Kirsch, C. Krug, P. Y. Hung, S. C. Song, B. S. Ju, J. Price, G. Pant, B. E. Gnade, W. Krautschneider, B.-H. Lee, and R. Jammy, "Tetragonal phase stabilization by doping as an enabler of thermally stable HfO<sub>2</sub> based MIM and MIS capacitors for sub 50 nm deep trench DRAM," in *IEDM Tech. Dig.*, 2006, p. 341 011.

- [12] B. F. Hung, K. C. Chiang, C. C. Huang, A. Chin, and S. P. McAlister, "High-performance poly-silicon TFTs incorporating LaAlO<sub>3</sub> as the gate dielectric," *IEEE Electron Device Lett.*, vol. 26, no. 6, pp. 384–386, Jun. 2005.

- [13] K. H. Lee, J. K. Park, and J. Jang, "A high-performance polycrystalline silicon thin film transistor with silicon nitride gate insulator," *IEEE Trans. Electron Devices*, vol. 45, no. 12, pp. 2548–2551, Dec. 1998.

- [14] I.-W. Wu, T. Y. Huang, W. B. Jackson, A. G. Lewis, and A. Chiang, "Passivation kinetics of two types of defects in polysilicon TFT by plasma hydrogenation," *IEEE Electron Device Lett.*, vol. 12, no. 4, pp. 181–183, Apr. 1991.

- [15] H.-C. Lin, K.-L. Yeh, M.-H. Lee, Y.-C. Su, T.-Y. Huang, S.-W. Shen, and H.-Y. Lin, "A novel methodology for extracting effective density-of-states in poly-Si thin-film transistors," in *IEDM Tech. Dig.*, 2004, pp. 781–784.

- [16] C. A. Dimitriadis, P. A. Coxon, L. Dozsa, L. Papadimitriou, and N. Economou, "Performance of thin-film transistors on polysilicon films grown by low-pressure chemical vapor deposition at various pressures," *IEEE Trans. Electron Devices*, vol. 39, no. 3, pp. 598–606, Mar. 1992.

- [17] T. Yamaguchi, R. Iijima, T. Ino, A. Nishiyama, H. Satake, and N. Fukushima, "Additional scattering effects for mobility degradation in Hf-silicate gate MISFETs," in *IEDM Tech. Dig.*, 2002, pp. 621–624.

- [18] P. D. Kirsch, M. A. Quevedo-Lopez, H.-J. Li, Y. Senzaki, J. J. Peterson, S. C. Song, S. A. Krishnan, N. Moumen, J. Barnett, G. Bersuker, P. Y. Hung, and B. H. Lee, "Nucleation and growth study of atomic layer deposited HfO<sub>2</sub> gate dielectrics resulting in improved scaling and electron mobility," *J. Appl. Phys.*, vol. 99, no. 2, p. 023 508, Jan. 2006.

- [19] A. Morioka, H. Watanabe, T. Mogami et al., "High mobility MISFET with low trapped charge in HfSiO films," in VLSI Symp. Tech. Dig., 2003, pp. 165–166.

- [20] C. F. Yeh, S. S. Lin, T. Z. Yang, C. L. Chen, and Y. C. Yang, "Performance and off-state current mechanisms of low-temperature processed polysilicon thin-film transistors with liquid phase deposited SiO<sub>2</sub> gate insulator," *IEEE Trans. Electron Devices*, vol. 41, no. 2, pp. 173–179, Feb. 1994.

- [21] C. T. Angelis, C. A. Dimitriadis, I. Samaras, J. Brini, G. Kamarinos, V. K. Gueorguiev, and T. E. Ivanov, "Study of leakage current in n-channel and p-channel polycrystalline silicon thin-film transistors by conduction and low frequency noise measurements," *J. Appl. Phys.*, vol. 82, no. 8, pp. 4095–4101, Oct. 1997.

- [22] M. Hack, I.-W. Wu, T. J. King, and A. G. Lewis, "Analysis of leakage currents in poly-silicon thin film transistors," in *IEDM Tech. Dig.*, 1993, pp. 385–388.

- [23] M. Yazaki, S. Takenaka, and H. Ohshima, "Conduction mechanism of leakage current observed in metal-oxide-semiconductor transistors and poly-Si thin-film transistors," *Jpn. J. Appl. Phys.*, vol. 31, no. 2A, pp. 206– 209. Feb. 1992.

- [24] C. H. Kim, K.-S. Sohn, and J. Jang, "Temperature dependent leakage currents in polycrystalline silicon thin film transistors," *J. Appl. Phys.*, vol. 81, no. 12, p. 8084, Jun. 1997.

- [25] S. Zafar, A. Callegari, E. Gusev, and M. V. Fischetti, "Charge trapping related threshold voltage instabilities in high permittivity gate dielectric stacks," *J. Appl. Phys.*, vol. 93, no. 11, pp. 9298–9303, Jun. 2003.

- [26] W.-T. Lu, P.-C. Lin, C.-H. Chien, M.-J. Yang, I.-J. Huang, P. Lehnen, and T.-Y. Huang, "The characteristics of hole trapping in HfO<sub>2</sub>/SiO<sub>2</sub> gate dielectrics with TiN gate electrode," *Appl. Phys. Lett.*, vol. 85, no. 16, pp. 3525–3527, Oct. 2004.

- [27] C. E. Blat, E. H. Nicollian, and E. H. Poindexter, "Mechanism of negative bias-temperature instability," *J. Appl. Phys.*, vol. 69, no. 3, pp. 1712–1720, Feb. 1991.

- [28] S. Ogawa and N. Shiono, "Generalized diffusion-reaction model for the low-field charge-buildup instability at the Si–SiO<sub>2</sub> interface," *Phys. Rev. B, Condens. Matter*, vol. 51, no. 7, pp. 4218–4230, Feb. 1995.

- [29] N. Kimizuka, K. Yamaguchi, K. Imai, T. Iizuka, C. T. Liu, R. C. Keller, and T. Horiuchi, "NBTI enhancement by nitrogen incorporation into ultrathin gate oxide for 0.1-\(\mu\)m gate CMOS generation," in VLSI Symp. Tech. Dig., 2000, pp. 92–93.

- [30] D. K. Schroder and J. A. Babcock, "Negative bias temperature instability: Road to cross in deep submicron silicon semiconductor manufacturing," *J. Appl. Phys.*, vol. 94, no. 1, pp. 1–18, Jul. 2003.

- [31] C.-Y. Chen, J.-W. Lee, S.-D. Wang, M.-S. Shieh, P.-H. Lee, W.-C. Chen, H.-Y. Lin, K.-L. Yeh, and T.-F. Lei, "Negative bias temperature instability in low-temperature polycrystalline silicon thin-film transistors," *IEEE Trans. Electron Devices*, vol. 53, no. 12, pp. 2993–3000, Dec. 2006.

- [32] J. Levinson, F. R. Shepherd, P. J. Scanlon, W. D. Westwood, G. Este, and M. Rider, "Conductivity behavior in polycrystalline semiconductor thin film transistors," *J. Appl. Phys.*, vol. 53, no. 2, pp. 1193–1202, Feb. 1982.

- [33] R. E. Proano, R. S. Misage, and D. G. Ast, "Development and electrical properties of undoped polycrystalline silicon thin-film transistor," *IEEE Trans. Electron Devices*, vol. 36, no. 9, pp. 1915–1922, Sep. 1989.

Ming-Jui Yang was born in Yi-Lan, Taiwan, R.O.C., on September 28, 1975. He received the B.S. and M.S. degrees in electronics engineering from National Chiao Tung University, Hsinchu, Taiwan, in 1997 and 1999, respectively, where he is currently working toward the Ph.D. degree in the Department of Electronics Engineering and Institute of Electronics.

Since 1999, he has been an Assistant Researcher with the National Nano Device Laboratory, Hsinchu. His research interest includes the high- $\kappa$  dielectrics

and advance low-temperature poly-Si TFTs for ultralarge-scale integration technologies and reliability analysis.

Chao-Hsin Chien (M'04–A'05) was born in 1968. He received the B.S., M.S., and Ph.D. degrees from National Chiao Tung University, Hsinchu, Taiwan, R.O.C., in 1990, 1992, and 1997, respectively, all in electronics engineering. His Ph.D. dissertation research focused on plasma-induced charging damage on deep-submicrometer devices with ultrathin gate oxides.

In 1999, he joined with the National Nano Device Laboratory, Hsinchu, where he is currently an Associate Researcher. He is also currently an Assistant

Professor with the Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University. His research interests and activities include high- $\kappa$  dielectric, novel nonvolatile memory devices, organic devices, and nanowire.

Yi-Hsien Lu was born in Yunlin, Taiwan, R.O.C., in 1983. He received the B.S. degree in physics from National Chung Hsing University, Taichung, Taiwan, in 2005 and the M.S. degree in electrophysics from National Chiao Tung University, Hsinchu, Taiwan, in 2007, where he is currently working toward the Ph.D. degree in the Institute of Electrophysics.

His current research topic is the fabrication and characterization of advance poly-Si TFTs.

**Chih-Yen Shen** was born in Pingtong, Taiwan, R.O.C., on December 23, 1980. He received the B.S. and M.S. degrees in chemical engineering from Chung-cheng University, Chia-yi, Taiwan, in 2003 and 2005, respectively.

Since 2006, he has been with the National Nano Device Laboratory, Hsinchu, Taiwan, where he worked in the metal organic chemical-vapor-deposition process about high- $\kappa$  materials. He is currently devoted to the research of high- $\kappa$  materials properties and applications.

**Tiao-Yuan Huang** (S'78–M'78–SM'88–F'95) received the B.S.E.E. and M.S.E.E. degrees from National Cheng Kung University, Tainan, Taiwan, R.O.C., in 1971 and 1973, respectively, and the Ph.D. degree from the University of New Mexico, Albuquerque, in 1981.

He has worked in the U.S. semiconductor industry for 14 years prior to his return to his native country, Taiwan. Since 1995, he has been a Professor with the Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University,

Hsinchu, Taiwan.

Dr. Huang was the recipient of the Semiconductor International's Technology Achievement Award for his invention and demonstration of the fully overlapped lightly doped drain MOS transistors.