## 行政院國家科學委員會專題研究計畫 成果報告

# 針對粗顆粒多重臨界電壓 CMOS 技術之電源開關繞線 研究成果報告(精簡版)

計畫類別:個別型

計 畫 編 號 : NSC 99-2221-E-009-186-

執 行 期 間 : 99年08月01日至100年07月31日 執 行 單 位 : 國立交通大學電子工程學系及電子研究所

計畫主持人: 趙家佐

報告 附件: 出席國際會議研究心得報告及發表論文

處 理 方 式 : 本計畫可公開查詢

中華民國100年10月19日

# 行政院國家科學委員會補助專題研究計畫成果報告

※※※※※※※※※※※※※※※※※※※※ 針對粗顆粒多重臨界電壓 CMOS 技術之電源開關繞線※※※※※※※※※※※※※※※※※※

計畫類別:■個別型計畫 □整合型計畫

計畫編號:99-2221-E-009-186

執行期間: 99年 8月 1日至100年 7月 31日

計畫主持人:趙家佐

共同主持人:

計畫參與人員:穆思邦、楊皓宇、陳擴安、郭淳仁、王易民、張玟翔、

徐浩文、黄欽遠

執行單位:交通大學電子工程系

中華民國 100年 10月 19日

## 針對粗顆粒多重臨界電壓 CMOS 技術之電源開關繞線

"Power-Switch Routing for Coarse-Grain MTCMOS Technologies" 計畫編號:NSC99-2221-E-009-186

執行期間:99年8月1日至100年7月31日

主持人:趙家佐 交通大學電子工程系副教授

#### 一、 中文摘要

關鍵詞:粗顆粒之多重臨界電壓 CMOS 技術(MTCMOS); MTCMOS 開關繞線;低功率設計;繞線;

多重臨界電壓 CMOS(MTCMOS)是一種有效的電源閘控制設計技術,藉由適當的交互使用高臨界電壓與低臨界電壓裝置,同時減低晶片之漏電流功率消耗,並維持晶片所需之表現。然而,現有的文獻當中,並無太多對於 MTCMOS 技術在後段工具演算法上的討論,而現階段 EDA 供應廠商,對於MTCMOS 技術的支援也還是不夠完整。

在這個計畫當中,我們要針對 TSMC 所使用的粗顆粒 MTCMOS 技術,設計一個 MTCMOS 開關繞線的軟體。這個開關繞線軟體的目標包含以下三點,第一,找到一條可行的漢米爾頓路徑(Hamiltonian path),並包含所有的 MTCMOS 開關,這樣所產生之回應訊號,可以保證所有的 MTCMOS 開關都有被打開;第二,要讓所有的 MTCMOS 開關之間的連線,都滿足預設的曼哈頓距離(Manhattan distance)限制,這樣所產生的 MTCMOS 開關之輸出負載,可以保證小於時間函數庫(timing library)所設定之上線;第三,將總繞線長度降到最低,這樣所產生之繞線負擔,以及喚醒(wake-up)/回應(acknowledge)訊號之回應時間,都可以被最小化。此外,所提出之 MTCMOS 開關繞線軟體必須能夠融入現有之後段設計流程中。

#### 英文摘要

Key words: coarse-grain MTCMOS, MTCMOS switch routing, low-power design, routing

In this project, we would like to propose a framework for MTCMOS switch routing based on the coarse-grain MTCMOS technologies provided by TSMC. The objective of this switch-routing framework is to (1) find a feasible Hamiltonian path covering all MTCMOS switches, such that its resulting acknowledge signal can guarantee the turn-on of all MTCMOS switches, (2) keep all connections between MTCMOS switches under the Manhattan-distance constraint, such that the output loading of a MTCMOS switch will not exceeds the constraint of its timing library, and (3) minimize the total routing length, such that the routing overhead as well as the response time of the wake-up/acknowledge signals can be minimized. Furthermore, the proposed MTCMOS switch-routing needs be compatible to the current design back-end flow.

#### 二、計畫緣由、目的、研究方法與實驗結果

#### 1. Introduction

As the process technologies continually scale down, IC's leakage power consumption has exponentially increased [1] [2] and greatly shortened the battery lifetime of portable, event-driven applications, such as cell phones, GPS, or PDAs, whose certain functions (mostly multi-media functions) are in the idle state most of the time. One solution to reduce this leakage power during the idle state is to use the power gating, which can completely shut down the power of the idle devices with header or footer switches and hence no leakage current is generated by those idle devices. However, the leakage current of

the switches or other always-on circuits still exists and should be further reduced.

By using both high-Vt and low-Vt transistors, Multi-threshold CMOS (MTCMOS) emerges to be an effective power-gating technique which can simultaneously reduce leakage power and maintain circuit performance. For an MTCMOS design, the header/footer switches and retention flip-flips are implemented in high-Vt transistors, such that their leakage current can be lowered during the sleep mode. On the other hand, the power-gated logics are implemented in low-Vt transistors, such that their performance can be increased during the active mode. The MTCMOS designs can be classified into two categories by its granularity: (1) fine-grain MTCMOS, in which one switch is built into each cell, and (2) coarse-grain MTCMOS, in which one switch is built to turn off a block of cells. In this project, we only focus on the discussion of the coarse-grain MTCMOS. A lot research effort has been put into the area of MTCMOS technologies during the past decade. One group of the research works focus on the MTCMOS power-gating structures, such as (1) the charge-recycling technique [3] [4], which can reduce the power consumption produced during the sleep-to-active mode transition, (2) the intermediate-mode switches [5], which can cover various demands of the power-performance trade-off, and (3) the distributed sleep-transistor network [6], which can effectively reduce the area overhead of sleep transistors. Another research aspect is to optimize different parameters under different constraints, such as circuit performance, mode-transition power consumption, power-supply noise, area overhead, and wake-up time, by using the sleep-transistor sizing [7] [8], circuit clustering [9], wake-up scheduling [10] [11], or simultaneous clustering and scheduling [12]. However, by our best knowledge, no previous work has discussed the required back-end algorithms supporting MTCMOS technologies.

A back-end tool for coarse-grain MTCMOS technologies should provide the following two functionalities: the switch allocation and the switch routing. In the MTCMOS design flow, designers first determine the area ratio of MTCMOS switches over the total cells based on the worst IR drop which can be tolerated on the power rails. A higher MTCMOS-switch ratio leads to a lower IR drop but, at the same time, a higher area overhead. Next, the switch allocation can determine the placement pattern and the spacing between adjacent MTCMOS switches based on the above area ratio of MTCMOS switches. Using the obtained placement pattern and spacing, the switch allocation then evenly distributes the MTCMOS switches over the entire IC except its hard macros, where no MTCMOS switches can be inserted. Thus, IC's floorplan should be finalized before distributing MTCMOS switches, but the placement of the gated low-Vt cells is not done yet.

After the location of each MTCMOS is determined, the switch routing will serially connect the sleep/wake-up signal of MTCMOS switches one by one. This serial connection can be viewed as a Hamiltonian path of MTCMOS switches. The main reason of using serial connection of MTCMOS switches instead of parallel connection is to reduce the rush current produced during sleep/active mode transition. Also, the signal at the end of the Hamiltonian path can be used as an acknowledgement signal, guaranteeing that all the MTCMOS switches are

successfully turned on. Besides finding a feasible Hamiltonian path of MTCMOS switches, the switch routing also attempt to minimize the length of the Hamiltonian path so that more routing resources can be left for the routing of low-Vt cells. However, not any pair of switches can be connected to each other. The Manhattan-distance between two connected switches has to be under a limit. Otherwise the loading added from the connection would violate the output-loading constraint of cell's timing library, resulting in an unpredictably long signal delay. In addition, the hard macros in the floorplan may break the regularity of switches' placement, which further increases the difficulty of finding a feasible Hamiltonian path of switches.

In this project, we develop a switch-routing framework for coarse-grain MTCMOS technologies, which first attempts to find a feasible Hamiltonian path covering all MTCMOS switches under the Manhattan-distance constraint and also minimize the length of the Hamiltonian path. If a feasible Hamiltonian path cannot be obtained, an acyclic trunk path covering a maximal number of switches will be reported along with branches covering the rest switches. The proposed switch-routing framework needs to take advantage of the location regularity of most switches, such that the path length can be minimized. Also the proposed framework needs to provide the flexibility to handle the location irregularity of some switches caused by hard macros, such that the resulting trunk path can cover maximal switches. In addition, the proposed switch-routing framework needs to be embedded in a design flow of the MTCMOS technology provided by an IC foundry [13]. We will conduct experiments on industrial MTCMOS designs to show that the proposed framework can effectively find a feasible Hamiltonian path with shorter length and shorter turn-on time. We will also compare the proposed framework with a state-of-the-art TSP solver (such as Concorde [15], GOBLIN [16], or LKH [17]).

#### 2. BACKGROUND

In this section, we introduce the MTCMOS technology and some related background information used in the proposed switch-routing framework. We focus on the discuss of MTCMOS designs using header switches. But the proposed framework can be easily applied to footer-switch MTCMOS designs in a similar manner.

#### 2.1. Architecture of MTCMOS Designs

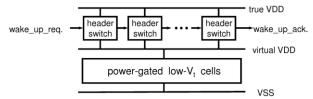

Figure 1 first illustrates the overview of an MTCMOS design using header switches. The power-gated low-V<sub>t</sub> cells are connected to the virtual VDD, whose power supply is controlled by the MTCMOS switches placed between the virtual VDD and true VDD. When the system turns on the wake-up-request signal, the header switches are turned on in order so that the virtual VDD can obtain the power from the true VDD. After the system receives the wake-up-acknowledge signal, the system starts to send jobs to the gated logics. When the system turns off the wake-up-request signal, the switches are turned off and the virtual VDD cannot provide any power to the gated cells, meaning that no leakage current can be generated on the gated cells.

Figure 1: MTCMOS power-supply architecture using header switches

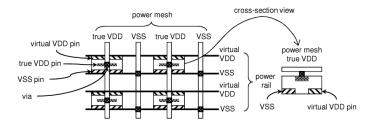

Figure 2 shows the physical layout of this power-supply architecture. On the vertical power meshes, the true VDD and VSS are alternatively provided. On the horizontal power rails, the virtual VDD and VSS are alternately provided, where an MTCMOS switch is placed to control the connection between a true-VDD mesh and a virtual-VDD rail. A VSS rail is directly connected to a VSS mesh through a via. Therefore, the location of an MTCMOS switch must be on the intersection of a vertical power mesh and a horizontal power rail. The spacing between two power rails depends on a standard cell's height and the spacing between two power mesh depends on the whole chip's power planning.

Figure 2: Physical layout of the MTCMOS power-supply architecture using header switches.

#### 2.2. Switch Allocation

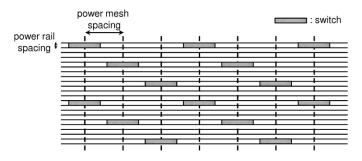

The area ratio of the MTCMOS switches over the total cells determines the IR drop on the power rails as well as the placement pattern for the switch allocation. The switch-placement pattern used in our MTCMOS designs is similar to Figure 3.

Figure 3: Placement pattern of MTCMOS switches.

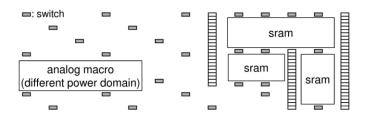

According to the switch-placement pattern, the switch allocation then evenly places the MTCMOS switches over the IC except the hard macros, where no switch can be inserted. If the encountered hard macro is an SRAM core or

any hard IP using the same power domain as the standard cells, extra switches are placed along the boundaries of the hard macro to strengthen its power supply. If the encountered hard macro is an analog IP, which has its own power domain, the switch-placement pattern around the boundaries remains the same. Figure 4 shows an exemplary switch allocation with hard macros. As a result, the regularity of the switch-placement pattern is broken by the hard macros.

Figure 4: Switch allocation with hard macros.

#### 2.3. MTCMOS Switches and Switch Routing

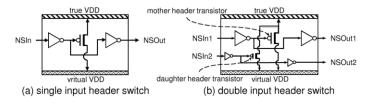

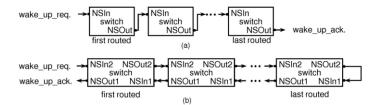

The coarse-grain library [13] provides two types of header switches: the single-input switches and double-input switches as showed in Figure 5(a) and 5(b), respectively, where all the inverters in Figure 5 are always-on and get their power directly from the true VDD. If the single-input switches are used, the switches are serially connected as Figure 6(a), where the N SI n signal of the first routed switch is connected to system's wakeup-request signal and the N SOut of the last routed switch is connected to the system's wake-up-acknowledge signal. Since the pins of wake-up-request and wake-up-acknowledge signals usually locate next to each other, the routed path of single input switches looks like a Hamiltonian cycle.

Figure 5: Types of MTCMOS header switches.

If the double-input switches are used, the switches are connected as Figure 6(b), where the wake-up-request and wake-up acknowledge signals are connected to the N SI n2 and N SOut1 signals of the first routed switch, respectively. Also, the N SOut2 signal of last routed switch is connected to the N SI n1 signal of itself. Therefore, the routed path of double-input switches looks like a Hamiltonian path. The routed path can end at any switch in the design.

Figure 6: Switch routing for (a) single-input and (b) double-input switches.

The double-input switches can reduce the power-up glitch current by first turning on a daughter header transistor with smaller driving capability and strengthen the power supply to the virtual VDD by then turning on a mother header transistor with larger driving capability. In our MTCMOS designs, we use double-input switches as recommended by [13].

#### 2.4. Manhattan-Distance Constraint

When connecting the next routed switch, designers have to make sure that the output loading of the current switch (or the input slew of the next routed switch) cannot exceed the upper bound of the timing library. Otherwise, the signal delay between two switches may be unpredictably long. One practical solution is to set a constraint on the Manhattan-distance between two connected switches based on metal's unit length loading and switch's intrinsic loading. This Manhattan-distance constraint has to be conservative since the detail routing path between two switches may detour due to routing congestion. In fact, this constraint is usually an empirical value and may vary from different designs and adopted APR tools.

#### 3. Problem Formulation

#### 3.1. Problem Formulation

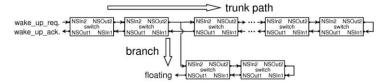

Given the result of the switch allocation, the switch routing is performed to find a routing path which can serially connect all the MTCMOS switches and satisfy the Manhattan-distance constraint. However, such Hamiltonian path covering all switches may not always exist in the given switch allocation or require prohibitively high computational complexity to obtain. Therefore, the first objective of the switch routing is to maximize the number of switches covered by the resulting routing path. For the uncovered switches, we add branches to the resulting path (also called trunk path in later discussion) to propagate the wake-up-request signal to them. However, the switches on the branches cannot send back a signal back to the wake-up-acknowledge signal. Figure 7 shows an example of adding a branch to the trunk path. As a result, when testing this MTCMOS IC, we cannot ensure whether the MTCMOS switches on the branch can be successfully turned on. This disadvantage on testing is the most important reason why the switch routing avoids the usage of branches and attempts to maximize the number of switches covered the trunk path.

Figure 7: Trunk path and branch for switch routing.

The second objective of the switch routing is to minimize the total length of the trunk path in terms of Manhattan-distance. A shorter trunk path can leave more routing resources for the routing of the gated low-\$V\_t\$ cells. Also, a shorter routing path can result in a shorter response time of the wake-up-acknowledge signal.

The problem formulation of the proposed switch-routing framework is summarized as follows.

#### Input:

- The location of each switch after switch allocation.

- The Manhattan-distance constraint between two connected switches.

- The starting location (the wake-up-req. signal). Output:

- A trunk path which visits each switch at most once.

- Branches which cover the switches not visited by the trunk path.

#### Objective:

- First priority: maximize the number of switches covered by the trunk path.

- Second priority: minimize the total length of the trunk path and branches in terms of Manhattan-distance.

#### 3.2. MTCMOS Switch Routing Using TSP Solver

Several TSP solvers have been developed in the past to find a Hamiltonian path with minimal length. However, current public TSP solvers (such as Concorde [15], GOBLIN [16], or LKH [17]) are all performed based on a complete graph, where any two nodes are connected to each other and a Hamiltonian path can always be easily found. Due to the Manhattan-distance constraint, the connection graph of MTCMOS switch routing is not complete and hence the existing TSP solver cannot be directly applied to solve the MTCMOS switch routing.

In order to do so, we try the following method based on a modified complete graph. First, we assign each edge's weight as the distance between the two switches of the edge if this distance is smaller than the given Manhattan-distance constraint. Then, to further lead the TSP result to satisfy the Manhattan-distance constraint, we assign an excessively large weight to each edge whose distance between its two switches exceeds the constraint. In our experiment, this excessively large weight is set to the summation of the distance between any two switches. In other words, as long

as any of those constraint-violated edges is included in the resulting Hamiltonian path, the length of the Hamiltonian path is guaranteed to be larger than that of a path including no constraint-violated edge. Therefore, while a TSP solver tries to minimize the path length, those constraint-violated edges should be avoided if the TSP algorithm is optimal enough.

Unfortunately, the TSP solvers we tried cannot lead to a Hamiltonian path without going through a constraint-violated edge. We will show the experimental results later in the project. This inefficiency of using an existing TSP solver to solve MTCMOS routing is actually one of our motivations to develop our own framework for MTCMOS switch routing.

#### 4. PROPOSED SWITCH-ROUTING FRAMEWORK

Basically, our switch-routing framework applies a greedy-based algorithm to find a minimal Hamiltonian trunk path of switches. The algorithm begins with a given starting point (the wake-up-req. signal) and each time selects the unvisited switch closest to the current switch as the next routed switch. Also, we utilize the following three techniques, the bridge creation (Section 4.2), the switch absorption (Section 4.3), and the rectangle routing (Section 4.4), to enhance algorithm's flexibility of finding a feasible Hamiltonian path and reduce total path length.

The bridge creation is applied when the distance from the current switch to its closest switch exceeds the Manhattan-distance constraint. The switch absorption is applied when using bridge creation may increase the total path length too much. The rectangle routing is applied to preserve some rectangles containing a maximal number of regularly-placed switches and then route the switches inside those rectangles with a minimal-length path. The data structure representing switch's location is shown in Section 4.1. The overall flow of the proposed switch-routing framework is summarized in Section 4.5.

#### 4.1. Data Structure for Switch's Location

In our switch-routing framework, we use a two-dimensional position matrix to record the location of switches. The elements on the same row (column) have the same coordinate in the X (Y) axis. If the value of an element is 1, a switch is located at the element's location. Otherwise, no switch exists on that location. The distance between each pair of adjacent rows (or columns) may not be the same and hence is recorded in another matrix, called distance matrix. The search for switches discussed in later subsections is performed based on the position and distance matrices. Note that we do not record the distance between each two switches to speed up the search of the closest switch. This is because the total number of switches in our MTCMOS design may be larger than 100K and the size of a  $N^2$  edge matrix may exceed our system's limitation.

#### 4.2. Bridge Creation

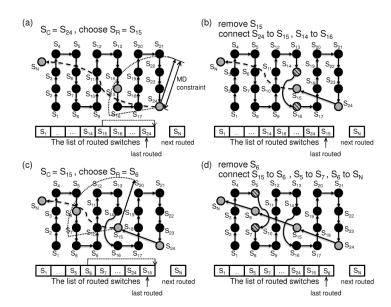

Since a greedy algorithm is applied to select the next routed switch of the trunk path, it is quite often that the resulting path goes to a dead end, from where the distance to the closest unvisited switch exceeds the Manhattan-distance constraint. In such cases, a bridge is created to connect the last routed switch  $S_{\rm C}$  to the next routed switch  $S_{\rm N}$  by removing some routed switches and using them as the intermediate switches between  $S_{\rm C}$  and  $S_{\rm N}$ . However, not every routed switch is removable. A routed switch  $S_{\rm R}$  is removable if  $MD(S_{\rm R-1},~S_{\rm R+1})$  satisfies the Manhattan-distance constraint, where  $MD(S_{\rm R-1},~S_{\rm R+1})$  denotes the Manhattan-distance between  $S_{\rm R}$  's ancestor switch  $S_{\rm R-1}$  and descendant switch  $S_{\rm R+1}$ .

In the bridge creation, we choose the next intermediate switch  $S_R$  as the removable switch satisfying the following two conditions: (1)  $MD(S_R, S_C)$  is under the Manhattan-distance constraint, and (2)  $MD(S_R, S_N)$  is as short as possible. Then we remove the intermediate switch SR from the trunk path, connect  $S_C$  to  $S_R$ , and connect  $S_R$ 's ancestor switch  $S_{R-1}$  to its descendant switch  $S_{R+1}$ . After such a modification, each connection in the trunk path still can satisfy the Manhattan-distance constraint and the last routed switch becomes  $S_R$ , which locates much closer to  $S_N$  than the original  $S_C$ . If the distance between  $S_R$  and  $S_N$  still exceeds the constraint, we repeat the above actions to find another proper intermediate switch closer to  $S_N$ .

Figure 8 shows an example of creating a bridge from  $S_{24}$  to  $S_N$ , where the sequence of the routed switches is  $S_1$ ,  $S_2$ ,...,  $S_{24}$ , and  $MD(S_{24}, S_N)$  exceeds the constraint. In Figure 8(a), we select the intermediate switch  $S_{15}$  following the above two conditions. Then we remove  $S_{15}$ , connect  $S_{24}$  to  $S_{15}$ , and connect  $S_{14}$  to  $S_{16}$  in Figure 8(b). After that, the last routed switch becomes  $S_{15}$  but  $MD(S_{15}, S_N)$  still exceeds the constraint. So, we select anther intermediate switch  $S_6$  in Figure 8(c). Next, we remove  $S_6$ , connect  $S_{15}$  to  $S_6$ , and connect  $S_5$  to  $S_7$  in Figure 8(d). Now, the distance between the last routed switch  $S_6$  and  $S_N$  can satisfy the constraint, and hence we can directly perform this switch absorption is that both  $MD(S_1, S_N)$  and  $MD(S_N, S_2)$  are under the Manhattan-distance constraint, and hence we can directly connect  $S_6$  to  $S_N$ .

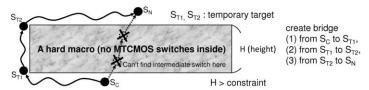

If the closest unvisited switch SN to the current switch SC is on the opposite side of a large hard macro such as Figure 9, then the above process of bridge creation may fail because it tends to select the intermediate switches locating between SC and SN. In this situation, we have to detour the way of selecting the intermediate switches along the boundary of the hard macro, such as Figure 9. Therefore, we select few removable routed switches at the rectangle's corners as temporary target switches. such as ST 1 and ST 2 in Figure 9. By creating bridges to temporary target switches, we can successfully connect to the real target switch SN. Note that, in this detour situation, the estimated distance from SC to SN should be the summation of M D(SC, ST 1), M D(ST 1, ST 2), and M D(ST 2, SN), instead of M D(SC, SN). Thus, before really creating a bridge to SN, we check whether the distance from SC to its second closest unvisited switch is shorter than this estimated distance to SN. If yes, we change the next routed switch to the second closest one. In addition, to complete the above detour, the location and the dimensions of each hard macro need to be recorded in advance so that we can efficiently check their existence before bridge creation.

Figure 8: An example of bridge creation.

Fig 9: Detour in bridge creation.

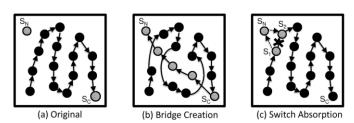

#### 4.3. Switch Absorption

At the late phase of the switch routing, some unvisited switches may scatter over the IC, such as SN in Figure 10(a). If we use bridge creation to connect it, the total path length may increase a lot, such as Figure 10(b). To economically connect a dangling unvisited switch SN, we can break an existing edge from S1 to S2 and then add another two edges from S1 to SN and from SN to S2, as shown in Figure 10(c). This operation looks like to absorb an unvisited switch into the routed trunk path and hence is called switch absorption. The premise to perform this switch absorption is that both M D(S1, SN) and M D(SN, S2) are under the Manhattan-distance constraint.

Fig 10: Difference between creation and switch absorption for routing a dangling switch.

To maximize the benefit of using switch absorption, two key problems remain to be solved: (1) when to apply switch absorption instead of bridge creation; (2) which switch to be absorbed first. To solve the first problem, we need to estimate the cost of performing each of switch absorption and bridge creation. The path length increased by creating a bridge to a target switch is usually higher than absorbing one switch. However, after the bridge is created, we may be able to route a group of unvisited switches close to the target switch with short edges, which can compensate the cost of creating the bridge. Therefore, the cost of creating a bridge should be the average edge length added before the next bridge creation (including the length of the current bridge).

In fact, at the early phase of switch routing, a lot unvisited switches can be routed after a bridge is created. Thus, we will not consider the use of switch absorption at all until a high percentage of switches are already routed (more specifically, 98% in our method), which can save the computational overhead of comparing the costs of bridge creation and switch absorption. Once using switch absorption, we stop using bridge creation and absorb all the remaining unvisited switches. Therefore, we compare the cost of creating a bridge with the average added length of absorbing each of the remaining switches.

The most possible way to absorb an unvisited switch is to break the edge either coming to or starting from its closest routed switch. Thus, the cost of absorbing the unvisited switch can be approximately estimated by the shorter added length of choosing either of the above two edges for absorption. To collect this absorption cost for all unvisited switches from scratch is expensive. Hence, for each unvisited switch, we record its closest routed switch, its distance to the closest routed switch, and its absorption cost. Each time a new switch is routed, we check whether its distance to each unvisited switch is smaller than its recorded closest distance. If yes, we update the closest-routed-switch information for the unvisited switch. If no, no change is made. Note that we start to record the above closest-routed-switch information when 98% of the switches are already routed. Its computational overhead is limited.

As to the second problem, the ordering of absorbed switches may affect its total added path length since the new absorbed switch may form a better edge to break for the later absorbed switches. Thus, we always absorb the switch with the shortest distance to its closest routed switch, leaving the other switches a chance of shortening their distance to their closest routed switch. Also, we maintain the same closest-routed-switch information as above to determine the next absorbed switch.

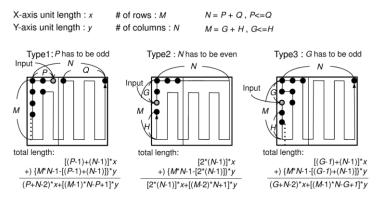

#### 4.4. Rectangle Routing

For a MTCMOS design, majority of the switches are placed regularly based on a placement pattern. To take advantage of this regularity, we first identify several maximal-size rectangles in which the switches are all regularly placed, meaning that the X-axis (or Y-axis) distance between any two adjacent switches is the same. Then we route all the switches inside a rectangle at once. In fact, the "rectangle" defined in our framework does not have a real rectangular shape physically due to the placement patterns, but we conceptually view it as a rectangle as shown in Figure 11. For such rectangles, a minimum Hamiltonian path covering all rectangle's switches can always be found efficiently.

Fig 11: (a) A conceptual rectangle used in our rectangle routing, and (b) the real location of the switches inside the rectangle.

In our framework, we use only the following three types of Hamiltonian-path routing to route the switches within a rectangle. Because the X-axis unit length (X-axis distance between two adjacent switches) is much longer than the Y-axis unit length in the used placement pattern, we try to avoid the traverse in X-axis as much as possible. With these three types of Hamiltonian-path routing, we can guarantee that the resulting Hamiltonian path within the rectangle has the shortest length given the input switch (the first routed switch). Once the routing type and the input switch is determined, its output switch (the last routed switch in the rectangle) is determined as well.

Figure 12 shows the three types of Hamiltonian-path routing and their corresponding path length on a M x N rectangle. When the input switch is on the top (or bottom) side of the rectangle, we apply the Type-1 routing. To use the Type-1 routing, P has to be odd, where P means that the input switch is the  $P_{th}$  switch on the top side counting from the closer right or left side. Therefore, an input switch with an even P will not be considered when the routing starts from the top side.

Fig 12: Rules for routing a single rectangle.

When the input switch is on the left (or right) side, we choose the proper routing between type-2 and type-3 routing. To apply type-2 routing, N has to be even, where N is number of rows. To apply type-3 routing, G has to be odd, where G means that the input switch is the  $G_{th}$  switch on the left side counting from the closer top or bottom side. If both type-2 and type-3 routing cannot be applied to an input switch, then that input switch will not be considered when the routing starts from the left side. If both type-2 and type-3 routing can be applied to an input switch, then both types will be considered for that input switch. Note that the total length for each type routing listed in Figure 12 is only an approximation (lower bound actually). The sawtooth-like top and bottom sides require a little extra length in

Y axis, which can be computed by a slightly more complicated equation. We omit this equation due to the page limitation.

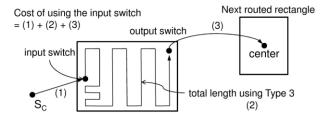

In our switch-routing framework, the rectangle routing is performed before the switch absorption. Also, the rectangle routing is performed after (1) most switches outside the rectangles are routed and (2) the creation bridge requires a higher cost than the average cost of switch absorption. The rectangle routing first determines the ordering of rectangles to be routed using a greedy algorithm. This greedy algorithm starts from the last routed switch SC, and each time selects the next routed rectangle whose center is closest to the center of the current rectangle (or SC at the first time). We route one rectangle at a time based on this rectangle ordering.

For each rectangle to be routed, we choose the best input switch along with a proper type of Hamiltonian-path routing which can minimize the summation of the following three distances: (1) the distance from the last routed switch SC to the rectangle's input switch, (2) the total path length within the rectangle according to the adopted routing type, and (3) the distance from the output switch of the current rectangle to the center of the next routed rectangle (as shown in Figure 13).

Fig 13: Chose the best input switch for a rectangle.

Note that the rectangles are viewed as hard macros before the rectangle routing. Thus, we need to determine which maximal-size rectangles are preserved for the rectangle routing at the beginning of the switch routing. More rectangles preserved for switch routing imply that more regularly placed switches can be routed in a local minimal way. However, at the same time, more obstacles exist when routing the switches outside the rectangles. So far we have not found an effective method to estimate which group of preserved rectangles can result in a minimal total length. Therefore, we first start from using no rectangle, and then each time add the rectangle covering most switches until adding the rectangle cannot further reduce the total length. Our experimental result will show that the proposed switch-routing framework is efficient enough to afford the iterative trials. In addition, when we estimate the average cost of switch absorption, the switches within the rectangles are considered routed since the switch absorption is performed after the rectangle routing.

#### 4.5. Overall Flow

Figure 14 summarizes the overall flow of the proposed switch-routing framework.

```

Algorithm: SwitchRouting

# define

MD(s1, s2): Manhattan distance between s1 and s2

Nearby(s): the switch closest to s

MD_constrain: Manhattan distance constraint

unvisit_ratio: the ratio of unvisited switches no in rectangles

threshold: user-specified ratio determining when to consider

switch absorption

cost\_bc(S_c, S_n): cost of creating a bridge from S_c to S_n

cost\_sa\_avg(): cost of absorbing S_n

Plist: List of path switches

1 begin

Build position matrix and matrix for all switches

3

Build hard macro records

S_c = \text{starting switch};

Append S_c to Plist;

while (any unvisited switch exists) {

S_n = Nearby(S_c)

if (MD(S_c, \check{S_n}) < MD\_constrain) {

8

9

append S_n to Plist; S_c = S_n;

10

11

else if (unvisit_ratio > threshold ||

12

cost\_bc(S_c, S_n) < cost\_sa\_avg()  {

create a bridge from S_c to S_n;

13

append S_n to Plist; S_c = S_n;

14

15

16

else if (rectangles not routed yet) {

route rectangles from S_c;

17

S_c becomes the last routed switch in rectangles;

18

19

20

else

21

break

22

try to absorb remaining switches into Plist if possible;

24 create branches to connect remaining switches;

```

Fig 14: The overall algorithm of the proposed switch-routing framework.

#### 5. Experimental RESULT

#### 5.1. Results of Proposed Framework

In this subsection, we first perform the proposed switch-routing frameworks on four industrial MTCMOS designs based on a 65nm coarse-grain MTCMOS technology [11] with 6 metal layers. Among those designs, Case 1 is already in production, containing 320 hard macros (including both power-gated and always-on macros) and more than 1-million instances (around 600K power-gated instances). The switch allocation is done semi-automatically with the back-end tool, Blast Fusion [12]. The Manhattan-distance constraint is set to 150µm.

Table 1 first shows the result of the proposed switch-routing framework using different numbers of rectangles. In Table 1, Column 2 and 3 list the total chip size and total number of MTCMOS switches, respectively. Column 4, 5, and 6 list the number of rectangles in use, the percentage of switches inside the rectangles, and the total Manhattan distance of the trunk path, respectively. A shadowed slot indicates the shortest path length of using different numbers of rectangles. Column 7 lists the percentage of switches covered by the trunk path. Column 8 lists the total runtime in seconds.

| design | chip size<br>(mm²) | # of<br>switches | # of<br>rect. | switch<br>% in | Total<br>MD | trunk path<br>coverage | Runtime<br>(sec) |

|--------|--------------------|------------------|---------------|----------------|-------------|------------------------|------------------|

|        |                    |                  |               | rect.          | (µm)        |                        |                  |

| Case 1 | 13.595             | 17523            | 0             | 0              | 257385      | 100%                   | 107              |

|        |                    |                  | 1             | 40.10          | 256425      | 100%                   | 90               |

|        |                    |                  | 2             | 53.03          | 256349      | 100%                   | 71               |

|        |                    |                  | 3             | 55.41          | 257042      | 100%                   | 73               |

| Case 2 | 13.552             | 20593            | 0             | 0              | 325196      | 100%                   | 102              |

|        |                    |                  | 1             | 39.14          | 323945      | 100%                   | 102              |

|        |                    |                  | 2             | 50.17          | 327959      | 100%                   | 112              |

|        |                    |                  | 3             | 51.27          | 326792      | 100%                   | 80               |

| Case 3 | 29.426             | 57035            | 0             | 0              | 853093      | 100%                   | 373              |

|        |                    |                  | 1             | 40.16          | 852055      | 100%                   | 181              |

|        |                    |                  | 2             | 58.09          | 850614      | 100%                   | 111              |

|        |                    |                  | 3             | 72.31          | 854374      | 100%                   | 150              |

| Case 4 | 66.234             | 173420           | 0             | 0              | 2570350     | 100%                   | 4139             |

|        |                    |                  | 1             | 39.04          | 2545080     | 100%                   | 1512             |

|        |                    |                  | 2             | 46.06          | 2548310     | 100%                   | 1589             |

|        |                    |                  | 3             | 52.14          | 2550770     | 100%                   | 1374             |

Table 1: Results of the proposed switch-routing framework on 4 industrial MTCMOS designs.

As the result shows, the proposed switch-routing framework can always find a feasible trunk path covering all the switches. Also, using only the largest one or two rectangles can already result in the shortest trunk path. It is because majority of the switches are regularly placed in real designs so that the largest two rectangles can cover around 50% of the total switches. In addition, the reported runtime demonstrates that the complexity of the proposed framework is scalable to large industrial designs, where the longest runtime is around 1.15 hours for routing 173K MTCMOS switches. Even we try the number of used rectangles from 0 to 3 respectively, the total runtime for the largest case is around 2.4 hours.

#### 5.2. Compared with Vendor Solution

In this subsection, we compare the proposed framework with a rough solution provided by an EDA vendor, which is a script file operating on the design database used in a back-end tool, not a tool's standard built-in function. Also, this solution does not consider the Manhattan-distance constraint. However, it is the only switch-routing solution we can get from our EDA vendor. Actually, one of our motivations to start developing the proposed switch-routing framework is from seeing the inefficiency of this rough vendor solution. The comparison results are reported in Table 2.

In Table 2, Column 3 and 4 list the total Manhattan distance of the trunk path and its number of violations against the Manhattan-distance constraint, respectively. Column 5 and 6 list the total wire length and the number of vias in use after detail route, respectively. Column 7 lists the path's response time from the wake-up-request signal to the wake-up-acknowledge signal. As the result shows, the proposed switch-routing framework performs better than the vendor's solution at every reported item. Note that the switch delay with an oversized output loading is estimated by using the linear extrapolation. The actual response time for the vendor's solution might be larger than the reported number shows.

| design | method   | total MD | # of MD   | wire length | # of via | response  |

|--------|----------|----------|-----------|-------------|----------|-----------|

|        |          | (µm)     | violation | (µm)        |          | time (µs) |

| Case 1 | vendor   | 922634   | 382       | 1907690     | 142625   | 7.87      |

|        | proposed | 256349   | 0         | 573513      | 142119   | 6.62      |

| Case 2 | vendor   | 908123   | 317       | 1892643     | 168948   | 8.53      |

|        | proposed | 323945   | 0         | 720615      | 167933   | 7.67      |

| Case 3 | vendor   | 1991841  | 429       | 4193585     | 475952   | 21.85     |

|        | proposed | 850614   | 0         | 1904906     | 464989   | 19.79     |

| Case 4 | vendor   | 5356878  | 580       | 11346593    | 1438786  | 63.28     |

|        | proposed | 2545080  | 0         | 5715291     | 1416614  | 58.50     |

Table 2: Comparison between the propose framework and a vendor solution.

#### 5.3. Compared with Vendor Solution

In this subsection, we attempt to solve the switch-routing problem by applying a TSP solver based on a modified complete graph as described in Section 3.2. Since we set an excessively large weight to each edge whose distance between its two switches exceeds the constraint, the TSP solver should avoid passing through such a constraint-violated edge while minimizing the total path length. If the TSP solver is optimal enough, no constraint-violated edge will be visited and hence a feasible Hamiltonian path can be found.

We first implement a simple greedy TSP algorithm, denoted as TSP1, which selects the unvisited switch closest to the current switch as its next ordered switch each time. Also, TSP1 will try several different initial switches individually. Among those trails, TSP1 reports the Hamiltonian path covering the least number of constraint-violated edges. The number of trials used in TSP1 is 0.1% of the total switches. Note that the search of the closest unvisited switch is done based on the same data structure as the proposed method (Section 4.1), such that we can avoid the use of a huge N<sup>2</sup> matrix for storing all edge's weight, where N is the total number of switches. Thus, the search of the closest unvisited switch in TSP1 may be relatively slow compared to the use of a N<sup>2</sup> edge matrix.

Table 3 compares the total Manhattan distance of the resulting Hamiltonian path, the number of constraint-violated edges, and the runtime between TSP1 and the proposed framework. As the result shows, the listed total Manhattan distance between TSP1 and the proposed framework is close. However, the path reported by TSP1 contains at least 24 more constraint-violated edges for each benchmark design. To eliminate all the constraint-violated edges from the reported path, a significant amount of Manhattan distance is needs be added to form a feasible Hamiltonian path. Also, the runtime of TSP1 is much longer than that of the proposed framework, especially for the largest design.

| design | method   | total MD<br>(µm) | # of MD<br>violation | runtime<br>(sec) |

|--------|----------|------------------|----------------------|------------------|

| Case 1 | TSP1     | 259218           | 24                   | 1008             |

|        | proposed | 256349           | 0                    | 71               |

| Case 2 | TSP1     | 321048           | 28                   | 1087             |

|        | proposed | 323945           | 0                    | 102              |

| Case 3 | TSP1     | 857110           | 26                   | 10298            |

|        | proposed | 850614           | 0                    | 111              |

| Case 4 | TSP1     | 2550120          | 32                   | 193379           |

|        | proposed | 2545080          | 0                    | 1512             |

Table 3: Comparison between the propose framework and a greedy-based TSP solver.

Next, we try to apply a state-of-the-art TSP solver [13] to solve the switch-routing problem and check whether this advanced TSP solver can generate a feasible Hamiltonian path without going through any constraint-violated edge. The TSP solver [13] can be obtained from public domain and has been applied to solve several optimization problems [16] [17] [18]. Also, this TSP solver [13] can always iteratively fine-tune an existing solution to obtain a better solution. However, this TSP solver [13] requires a two-dimensional matrix to store all edges' weight of the complete graph.

Table 4 first lists the size of the edge matrix. For Case 3 and 4, the size of their edge matrices exceeds the limitation of the TSP solver [13] (as well as the main-memory size of our system) and hence no result can be obtained. For Case 1 and 2, the resulting path reported by the TSP solver [13] still contains few edges violating the constraint after running for more than 24 hours. This result demonstrates that a feasible short Hamiltonian path, which can be efficiently and effectively obtained by the proposed switch-routing framework, is not easy to be obtained by using a general TSP solver. It also shows the advantage of developing a heuristic algorithm which is specialized for solving MTCMOS switch routing and can utilize the physical-layout information of the MTCMOS switches.

| design                    | Case 1 | Case 2 | Case 3  | Case 4   |

|---------------------------|--------|--------|---------|----------|

| required edge-matrix size | 1.3 GB | 1.9 GB | 14.3 GB | 141.0 GB |

| # of left MD violation    | 2      | 2      | N.A.    | N.A.     |

Table 4: Required matrix size and the number of left violations against the Manhattan-distance constraint after running 24 hours for [13].

#### 三、結論

In this project, we proposed a switch-routing framework, which utilizes the techniques of the bridge creation, the switch absorption, and the rectangle routing to simultaneously minimize the trunk-path length and satisfy the Manhattan-distance constraint. The experimental result demonstrates its efficiency and effectiveness by comparing to a vendor solution and TSP solvers based on four industrial MTCMOS designs. This framework is ready to apply to the current MTCMOS design flow.

#### 四、參考文獻

- [1] K. Roy, S. Mukhopadhyay, and H. Mahmoodi-Meimand, " Leakage Current Mechanisms and Leakage Reduction Techniques in Deep-Submicrometer CMOS Circuits," Proceeding of the IEEE, vol. 91, No. 2, Feb. 2003, pp. 305-327

- [2] J. Kao, S. Narendra, and A. Chandrakasan, Subthreshold Leakage Modeling and Reduction Techniques, ACM/IEEE International Conference on Computer Aided Design, pp.141-148, Nov., 2002.

- [3] Z. Liu and V. Kursun, Charge Recycling Between Virtual Power and Ground Lines for Low Energy MTCMOS, IEEE/ACM International Symposium on Quality Electronic Design, pp.239-244, March 2007.

- [4] E. Pakbaznia, F. Fallah, and M. Pedram, Charge Recycling in MTCMOS Circuits: Concept and Analysis, Design Automation Conference, pp.97-102, July 2006.

- [5] S. Kim, S. V. Kosonocky, D. R. Knebel, and K. Stawiasz, Experimental Measurement of a Novel Power Gating Structure with Intermediate Power Saving Mode, International Symposium on Low Power Electronics and Design, pp.20-25, Aug. 2004.

- [6] C. Long and L. He, Distributed Sleep Transistors Network for Power Reduction, Design Automation Conference, pp.181-186, July 2003.

- [7] J. Kao, S. Narendra, and A. Chandrakasan, MTCMOS Hierarchical Sizing based on Mutual Exclusive Discharge Patterns, Design Automation Conference, pp.495-500, June 1997

- [8] C. Hwang, C. Kang, and M. Pedram, Gate Sizing and Replication to Minimize the Effects of Virtual Ground Parasitic Resistances in MTCMOS Designs, IEEE/ACM International Symposium on Quality Electronic Design, March 2006.

- [9] M. Anis, S. Areibi, and M Elmasry, Design and Optimization of Multithreshold CMOS (MTCMOS) Circuits, IEEE Trans. on Computer-Aided Design of Integrated Circuits and Systems, pp.1324-1342, Volume 22, Issue 10, Oct. 2003.

- [10] Ramalingam, A. Devgan, and D. Z. Pan, Wakeup Scheduling in MTCMOS Circuits Using Successive Relaxation to Minimize Ground Bounce, Journal of Low Power Electronics, pp.1-8, Vol.3, No.1, 2007.

- [11] H. Jiang and M. Marek-Sadowska, Power Gating Scheduling for Power/Ground Noise Reduction, Design Automation Conference, pp.980-985, June 2008.

- [12] Abdollahi, F. Fallah, and M. Pedram, A Robust Power Gating Structure and Power Mode Transition Strategy for MTCMOS Design, IEEE Trans. on Very Large Scale Integration Systems, pp.80-89, Volume 15, Issue 1, Jan. 2007.

- [13] Taiwan Semiconductor Manufacturing Company, Ltd., TSMC Reference Flow 7.0, 2007.

- [14] Magma Design Automation, Blast Fusion User Guide Version: 2005.03, June 2007.

- [15] D. Applegate, R. Bixby, V. Chvatal, and W. Cook Concorde TSP Solver, http://www.tsp.gatech.edu/concorde/index.html.

- [16] C. Fremuth-Paeger, B. Schmidt, and B. Eisermann, GOBLIN: A Graph Object Library for Network Programming Problems, <a href="http://www.math.uni-augsburg.de/fremuth/goblin.html">http://www.math.uni-augsburg.de/fremuth/goblin.html</a>.

- [17] K. Helsgaun, LKH: An Effective Implementation of the Lin-Kernighan Heuristic for solving TSP, <a href="http://akira.ruc.dk/">http://akira.ruc.dk/</a> keld/research/LKH/.

- [18] D. Aldous and A. G. Percus, Scaling and Universality in Continuous Length Combinatorial Optimization, PROC. Nat. Acad. Sci. USA 100 (20), pp.11211-11215, 2003.

- [19] D. Applegate, W. Cook, S. Dash, and A. Rohe, Solution of a Min-Max Vehicle Routing Problem, INFORMS Journal on Computing 14 (2), pp.132-143, 2002.

[20] G. Guti n, H. Jakubowicz, S. Ronen, and A. Zverovitch, Seismic Vessel Problem, Communications in DQM 8, pp.13-20, 2005.

### 行政院國家科學委員會補助國內專家學者出席國際學術會議報告

2010年11月20日

| 報告人姓名          | 趙家佐                                                                                                                                             | 服務機構 及職稱 | 國立交通大學<br>電子工程學系          |  |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------------|--|--|

| 時間<br>會議<br>地點 | 10/31/2010~11/5/2010<br>Austin, TX, USA                                                                                                         | 本會核定補助文號 | 計畫編號 NSC99-2221-E-009-186 |  |  |

| 會議 名稱          | 2010 IEEE International Test Conference                                                                                                         |          |                           |  |  |

| 發表<br>論文<br>題目 | Mask versus Schematic – An Enhanced Design-Verification Flow for First Silicon Success     Fault Models and Test Methods for Subthreshold SRAMs |          |                           |  |  |

#### 一、參與會議經過:

ITC10 在美國德州 Austin 舉行,共有 25 場 technical session, 4 場 industrial practice, 5 場 panel, 1 場 poster session。 本次參加最主要的目地是論文報告,在 Session 13 "FM AND YIELD-LEARNING VIA DESIGN AND DATA"以及 Session 15 "MEMORY TESTING"。其餘參與之 session 有"DFT ADVANCES", "3-D TEST", "MEMORY ONLINE TEST AND FAULT TOLERANCE", "DETECTING AND UNDERSTANDING DEFECTS", "NEW ISSUES AND ENHANCEMENTS TO IEEE 1149.1", "CHARACTERIZE! VARIABILITY, DEFECTS, BIO-FLUIDICS", "SOFT-ERROR TOLERANCE AND MULTICORE TESTING"。

#### 二、與會心得

本會議為 VLSI Testing 最重要的會議,論文受重視度高,參展廠商多,涵概研究領域新穎,台灣在 2010 年的論文數目為 3。參與人員業界學界各占一半,所以不會僅限於單純的學術交流,很適合拓展研究視野。另外 poster session 的討論也相當踴躍,應該多鼓勵學生參與。

#### 三、建議

以後只要經費許可,應多鼓勵學生參與,特別是做 VLSI testing 領域的博士生,應該藉此機會了解測試領域最先進的研究成果,藉此刺激對研究工作的嚮往,並擴展國際學生之間交流。

| 四、攜回資料名稱及內容:<br>攜回一 CD 論文集 |   |  |

|----------------------------|---|--|

| 五、其他                       | 無 |  |

# 國科會補助計畫衍生研發成果推廣資料表

日期:2011/10/19

國科會補助計畫

計畫名稱:針對粗顆粒多重臨界電壓CMOS技術之電源開關繞線

計畫主持人: 趙家佐

計畫編號: 99-2221-E-009-186- 學門領域: 積體電路及系統設計

無研發成果推廣資料

# 99 年度專題研究計畫研究成果彙整表

計畫主持人:趙家佐 計畫編號:99-2221-E-009-186-

計畫名稱:針對粗顆粒多重臨界電壓 CMOS 技術之電源開關繞線

| 計畫名稱:針對粗顆粒多重臨界電壓 CMOS 技術之電源開關繞線 |                 |           |                         |                |      |     |                                            |

|---------------------------------|-----------------|-----------|-------------------------|----------------|------|-----|--------------------------------------------|

|                                 |                 |           |                         | 量化             |      |     | 備註(質化說                                     |

| 成果項目                            |                 |           | 實際已達成<br>數(被接受<br>或已發表) | 171771115 0771 |      | 單位  | 明:如數個計畫<br>共同成果、成果<br>列為該期刊之<br>對面故事<br>等) |

|                                 |                 | 期刊論文      | 0                       | 0              | 100% |     |                                            |

|                                 | <b>办上站</b>      | 研究報告/技術報告 | 0                       | 0              | 100% | 篇   |                                            |

|                                 | 論文著作            | 研討會論文     | 1                       | 1              | 100% |     |                                            |

|                                 |                 | 專書        | 0                       | 0              | 100% |     |                                            |

|                                 | 專利              | 申請中件數     | 0                       | 0              | 100% | 件   |                                            |

|                                 | <del>等</del> 利  | 已獲得件數     | 0                       | 0              | 100% | 17  |                                            |

| 國內                              | 11 11 45 15     | 件數        | 0                       | 0              | 100% | 件   |                                            |

|                                 | 技術移轉            | 權利金       | 0                       | 0              | 100% | 千元  |                                            |

|                                 | 參與計畫人力<br>(本國籍) | 碩士生       | 6                       | 6              | 100% | 人次  |                                            |

|                                 |                 | 博士生       | 2                       | 2              | 100% |     |                                            |

|                                 |                 | 博士後研究員    | 0                       | 0              | 100% |     |                                            |

|                                 |                 | 專任助理      | 0                       | 0              | 100% |     |                                            |

|                                 | 論文著作            | 期刊論文      | 0                       | 0              | 100% |     |                                            |

|                                 |                 | 研究報告/技術報告 | 0                       | 0              | 100% | 篇   |                                            |

|                                 |                 | 研討會論文     | 1                       | 1              | 100% |     |                                            |

|                                 |                 | 專書        | 0                       | 0              | 100% | 章/本 |                                            |

|                                 | 專利              | 申請中件數     | 0                       | 0              | 100% | 件   |                                            |

| 151 A                           | 47/1            | 已獲得件數     | 0                       | 0              | 100% | ''  |                                            |

| 國外                              | 技術移轉            | 件數        | 0                       | 0              | 100% | 件   |                                            |

|                                 | 1X 117 17 TT    | 權利金       | 0                       | 0              | 100% | 千元  |                                            |

|                                 |                 | 碩士生       | 6                       | 6              | 100% | 人次  |                                            |

|                                 | 參與計畫人力          | 博士生       | 2                       | 2              | 100% |     |                                            |

|                                 | (外國籍)           | 博士後研究員    | 0                       | 0              | 100% |     |                                            |

|                                 |                 | 專任助理      | 0                       | 0              | 100% |     |                                            |

無

列。)

|    | 成果項目            | 量化 | 名稱或內容性質簡述 |

|----|-----------------|----|-----------|

| 科  | 測驗工具(含質性與量性)    | 0  |           |

| 教  | 課程/模組           | 0  |           |

| 處  | 電腦及網路系統或工具      | 0  |           |

| 計畫 | 教材              | 0  |           |

| 重加 | 舉辦之活動/競賽        | 0  |           |

|    | 研討會/工作坊         | 0  |           |

| 項  | 電子報、網站          | 0  |           |

| 目  | 計畫成果推廣之參與(閱聽)人數 | 0  |           |

# 國科會補助專題研究計畫成果報告自評表

請就研究內容與原計畫相符程度、達成預期目標情況、研究成果之學術或應用價值(簡要敘述成果所代表之意義、價值、影響或進一步發展之可能性)、是否適合在學術期刊發表或申請專利、主要發現或其他有關價值等,作一綜合評估。

| 1.       | 請就研究內容與原計畫相符程度、達成預期目標情況作一綜合評估                                                       |

|----------|-------------------------------------------------------------------------------------|

|          | ■達成目標                                                                               |

|          | □未達成目標(請說明,以100字為限)                                                                 |

|          | □實驗失敗                                                                               |

|          | □因故實驗中斷                                                                             |

|          | □其他原因                                                                               |

|          | 說明:                                                                                 |

| 2.       | 研究成果在學術期刊發表或申請專利等情形:                                                                |

|          | 論文:■已發表 □未發表之文稿 □撰寫中 □無                                                             |

|          | 專利:□已獲得 □申請中 ■無                                                                     |

|          | 技轉:□已技轉 □洽談中 ■無                                                                     |

|          | 其他:(以100字為限)                                                                        |

|          | Tsun-Ming Tseng, Mango CT. Chao, Chien-Pang Lu, Chen-Hsing Lo, 'Power-Switch        |

|          | uting for Coarse-Grain MTCMOS Technologies', ACM/IEEE International Conference      |

| OH       | Computer Aided Design (ICCAD), pp. 39-46, 2009                                      |

|          | Tsun-Ming Tseng, Yi-Min Wang, Mango CT. Chao, Chien-Pang Lu, ' Power-Switch         |

| Roi      | uting for Coarse-Grain MTCMOS Technologies', VLSI Design/CAD Symposium, 2010        |

| <u> </u> | <b>建</b> 人 留 /                                                                      |

| ა.       | 請依學術成就、技術創新、社會影響等方面,評估研究成果之學術或應用價值(簡冊分法式用於公表力音差、價值、影鄉式洗一些發展力可能做)(以                  |

|          | 值(簡要敘述成果所代表之意義、價值、影響或進一步發展之可能性)(以 500字為限)                                           |

|          |                                                                                     |

|          | In this project, we proposed a switch-routing framework, which utilizes the         |

|          | techniques of the bridge creation, the switch absorption, and the rectangle routing |

|          | to simultaneously minimize the trunk-path length and satisfy the                    |

|          | Manhattan-distance constraint. The experimental result demonstrates its             |

|          | efficiency and effectiveness by comparing to a vendor solution and TSP solvers      |

|          | based on four industrial MTCMOS designs. This framework is ready to apply to the    |

|          | current MTCMOS design flow.                                                         |